US 20130321383A1

## (19) United States

# (12) Patent Application Publication UCHINO et al.

# (10) Pub. No.: US 2013/0321383 A1

### (43) **Pub. Date:** Dec. 5, 2013

# (54) PIXEL CIRCUIT, DISPLAY DEVICE, AND METHOD OF DRIVING PIXEL CIRCUIT

- (71) Applicant: Sony Corporation, Tokyo (JP)

- (72) Inventors: Katsuhide UCHINO, Kanagawa (JP); Junichi Yamashita, Tokyo (JP); Tetsuro Yamamoto, Kanagawa (JP)

- ramamoto, Kanagawa (JP)

- (73) Assignee: Sony Corporation, Tokyo (JP)

- (21) Appl. No.: 13/960,229

- (22) Filed: Aug. 6, 2013

### Related U.S. Application Data

- (63) Continuation of application No. 13/416,243, filed on Mar. 9, 2012, which is a continuation of application No. 10/557,800, filed on Nov. 16, 2006, now Pat. No. 8,149,185, filed as application No. PCT/JP04/07304 on May 21, 2004.

- (30) Foreign Application Priority Data

May 23, 2003 (JP) ...... 2003-146758

#### **Publication Classification**

- (51) Int. Cl. G09G 3/30 (2006.01)

### (57) ABSTRACT

A pixel circuit, display device, and method of driving a pixel circuit enabling source-follower output with no deterioration of luminance even with a change of the current-voltage characteristic of the light emitting element along with elapse, enabling a source-follower circuit of n-channel transistors, and able to use an n-channel transistor as an EL drive transistor while using current anode-cathode electrodes, wherein a source of a TFT 111 as a drive transistor is connected to an anode of a light emitting element 114, a drain is connected to a power source potential VCC, a capacitor C111 is connected between a gate and source of the TFT 111, and a source potential of the TFT 111 is connected to a fixed potential through a TFT 113 as a switching transistor.

### Background Art

FIG. 2

Background Art

<u>2a</u>

FIG. 3

Background Art

FIG. 4

Background Art

FIG. 5

Background Art

FIG. 6

Background Art

FIG. 7 Background Art

ND111 Ids V<sub>cc</sub> ND112 C111 C111 ~ DTL101 Κin V. -ND111 FIG. 10B ND112 ND112 ~ DTL101 C111 ~DTL101 Ż. <u>د</u>ة Ids V<sub>cc</sub> Vcc ND112 GND C111 → DTL101 ~DTL101 C111 INPUT SIGNAL

FIG. 16

FIG. 21

FIG. 26

FIG. 27

FIG. 28

FIG. 33

FIG. 34

FIG. 35

WSCN 404 WSL401 400 WSL 40m DSCN 3 407 DSL 42m PXLC PXLC 401 FIG. 36 PXLC HSEL 405 401 PXLC PXLC DSL40m WSL41m WSL 411 403 ~ DSCN 2 406 DSL 401 DSCN 1

FIG. 39

## PIXEL CIRCUIT, DISPLAY DEVICE, AND METHOD OF DRIVING PIXEL CIRCUIT

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation application of U.S. Ser. No. 13/416,243 filed Mar. 9, 2012, which is a continuation application of U.S. Ser. No. 10/557,800 filed Nov. 16, 2006, the entire contents of each of which are incorporated herein by reference. U.S. Ser. No. 10/557,800 is a National Stage of PCT/JP04/07304 filed May 21, 2004, and claims priority to Japanese Application No. 2003-146758 filed May 23, 2003.

## TECHNICAL FIELD

[0002] The present invention relates to a pixel circuit having an electro-optic element with a luminance controlled by a current value in an organic EL (electroluminescence) display etc., an image display device comprised of such pixel circuits arrayed in a matrix, in particular a so-called active matrix type image display device controlled in value of current flowing through the electro-optic elements by insulating gate type field effect transistors provided inside the pixel circuits, and a method of driving a pixel circuit.

#### BACKGROUND ART

[0003] In an image display device, for example, a liquid crystal display, a large number of pixels are arranged in a matrix and the light intensity is controlled for every pixel in accordance with the image information to be displayed so as to display an image.

[0004] This same is true for an organic EL display etc. An organic EL display is a so-called self-light emitting type display having a light emitting element in each pixel circuit and has the advantages that the viewability of the image is higher in comparison with a liquid crystal display, a backlight is unnecessary, the response speed is high, etc.

[0005] Further, it greatly differs from a liquid crystal display etc. in the point that the gradations of the color generation are obtained by controlling the luminance of each light emitting element by the value of the current flowing through the light emitting element, that is, each light emitting element is a current controlled type.

[0006] An organic EL display, in the same way as a liquid crystal display, may be driven by a simple matrix and an active matrix system. While the former has a simple structure, it has the problem that realization of a large sized and high definition display is difficult. For this reason, much effort is being devoted to development of the active matrix system of controlling the current flowing through the light emitting element inside each pixel circuit by an active element provided inside the pixel circuit, generally, a TFT (thin film transistor).

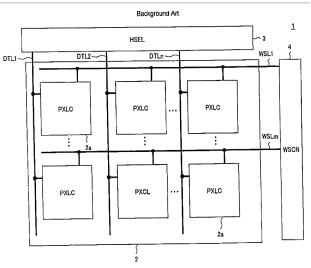

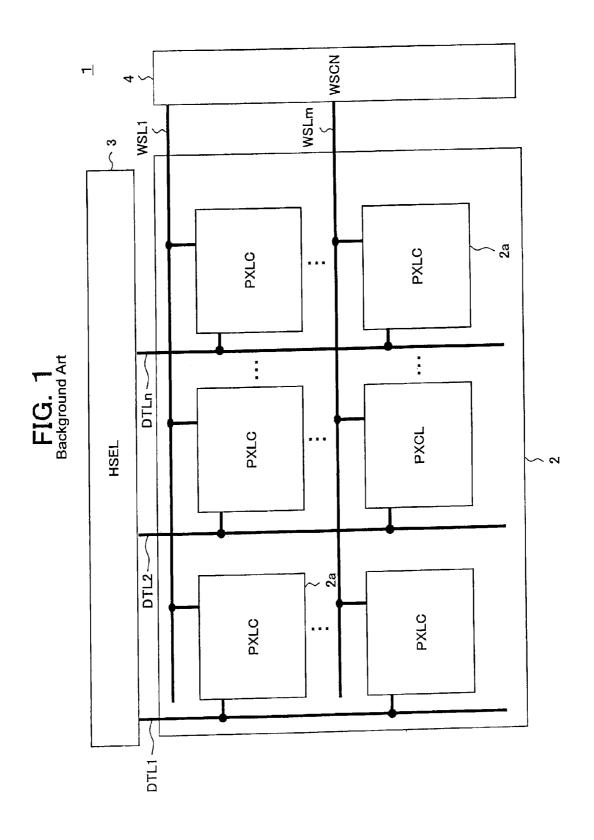

[0007] FIG. 1 is a block diagram of the configuration of a general organic EL display device.

[0008] This display device 1 has, as shown in FIG. 1, a pixel array portion 2 comprised of pixel circuits (PXLC) 2a arranged in an m×n matrix, a horizontal selector (HSEL) 3, a write scanner (WSCN) 4, data lines DTL1 to DTLn selected by the horizontal selector 3 and supplied with a data signal in accordance with the luminance information, and scanning lines WSL1 to WSLm selectively driven by the write scanner

[0009] Note that the horizontal selector 3 and the write scanner 4 are sometimes formed around the pixels by MOSICs etc. when formed on polycrystalline silicon.

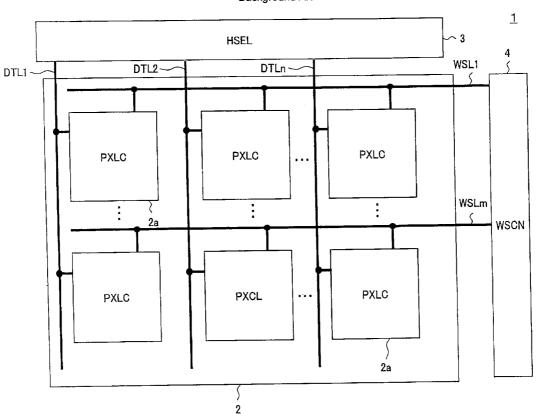

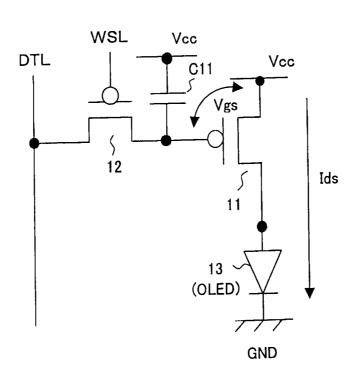

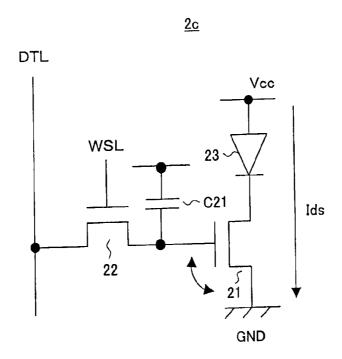

[0010] FIG. 2 is a circuit diagram of an example of the configuration of a pixel circuit 2a of FIG. 1 (refer to for example U.S. Pat. No. 5,684,365 and Patent Publication 2: Japanese Unexamined Patent Publication (Kokai) No. 8-234683).

[0011] The pixel circuit of FIG. 2 has the simplest circuit configuration among the large number of proposed circuits and is a so-called two-transistor drive type circuit.

[0012] The pixel circuit 2a of FIG. 2 has a p-channel thin film FET (hereinafter, referred to as TFT) 11 and TFT 12, a capacitor C11, and a light emitting element constituted by an organic EL element (OLED) 13. Further, in FIG. 2, DTL indicates a data line, and WSL indicates a scanning line.

[0013] An organic EL element has a rectification property in many cases, so sometimes is referred to as an OLED (organic light emitting diode). The symbol of a diode is used as the light emitting element in FIG. 2 and the other figures, but a rectification property is not always required for an OLED in the following explanation.

[0014] In the pixel circuit 2a of FIG. 2, a source of the TFT 11 is connected to a power source potential VCC, and a cathode of the light emitting element 13 is connected to a ground potential GND. The operation of the pixel circuit 2a of FIG. 2 is as follows.

[0015] <Step ST1>:

[0016] When the scanning line WSL is made a selected state (low level here) and a write potential V data is supplied to the data line DTL, the TFT 12 becomes conductive, the capacitor C11 is charged or discharged, and the gate potential of the TFT 11 becomes V data.

[0017] <Step ST2>:

[0018] When the scanning line WSL is made a non-selected state (high level here), the data line DTL and the TFT 11 are electrically separated, but the gate potential of the TFT 11 is held stably by the capacitor C11.

[0019] <Step ST3>:

[0020] The current flowing through the TFT 11 and the light emitting element 13 becomes a value in accordance with a gate-source voltage Vgs of the TFT 11, while the light emitting element 13 is continuously emitting light with a luminance in accordance with the current value.

[0021] As in the above step ST1, the operation of selecting the scanning line WSL and transmitting the luminance information given to the data line to the inside of a pixel will be referred to as "writing" below.

[0022] As explained above, in the pixel circuit 2a of FIG. 2, if once the Vdata is written, the light emitting element 13 continues to emit light with a constant luminance in the period up to the next rewrite operation.

[0023] As explained above, in the pixel circuit 2a, by changing a gate application voltage of the drive transistor constituted by the TFT 11, the value of the current flowing through the EL element 13 is controlled.

[0024] At this time, the source of the p-channel drive transistor is connected to the power source potential Vcc, so this TFT 11 is always operating in a saturated region.

[0025] Accordingly, it becomes a constant current source having a value shown in the following equation 1.

[0026] Here,  $\mu$  indicates the mobility of a carrier, Cox indicates a gate capacitance per unit area, W indicates a gate width, L indicates a gate length, and Vth indicates the threshold value of the TFT 11.

[0027] In a simple matrix type image display device, each light emitting element emits light only at a selected instant, while in an active matrix, as explained above, each light emitting element continues emitting light even after the end of the write operation. Therefore, it becomes advantageous in especially a large sized and high definition display in the point that the peak luminance and peak current of each light emitting element can be lowered in comparison with a simple matrix.

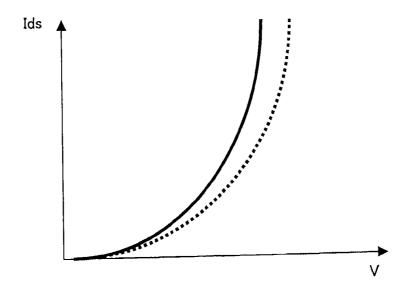

[0028] FIG. 3 is a view of the change along with elapse of the current-voltage (I-V) characteristic of an organic EL element. In FIG. 3, the curve shown by the solid line indicates the characteristic in the initial state, while the curve shown by the broken line indicates the characteristic after change with elapse.

[0029] In general, the I-V characteristic of an organic EL element ends up deteriorating along with elapse as shown in FIG. 3

[0030] However, since the two-transistor drive system of FIG. 2 is a constant current drive system, a constant current is continuously supplied to the organic EL element as explained above. Even if the I-V characteristic of the organic EL element deteriorates, the luminance of the emitted light will not change along with elapse.

[0031] The pixel circuit 2a of FIG. 2 is comprised of p-channel TFTs, but if it were possible to configure it by n-channel TFTs, it would be possible to use an amorphous silicon (a-Si) process in the past in the fabrication of the TFTs. This would enable a reduction in the cost of TFT boards.

[0032] Next, consider a pixel circuit replacing the transistors with n-channel TFTs.

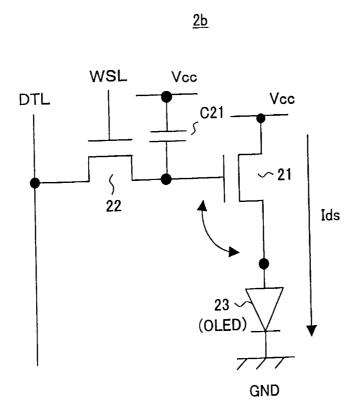

[0033] FIG. 4 is a circuit diagram of a pixel circuit replacing the p-channel TFTs of the circuit of FIG. 2 with n-channel TFTs.

[0034] The pixel circuit 2b of FIG. 4 has an n-channel TFT 21 and TFT 22, a capacitor C21, and a light emitting element constituted by an organic EL element (OLED) 23. Further, in FIG. 4, DTL indicates a data line, and WSL indicates a scanning line.

[0035] In the pixel circuit 2b, the drain side of the drive transistor constituted by the TFT 21 is connected to the power source potential Vcc, and the source is connected to the anode of the organic EL light emitting element 23, whereby a source-follower circuit is formed.

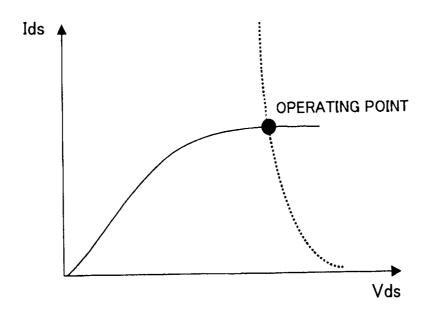

[0036] FIG. 5 is a view of the operating point of a drive transistor constituted by the TFT 21 and an EL element 23 in the initial state. In FIG. 5, the abscissa indicates the drain-source voltage Vds of the TFT 21, while the ordinate indicates the drain-source current Ids.

[0037] As shown in FIG. 5, the source voltage is determined by the operating point of the drive transistor constituted by the TFT 21 and the EL light emitting element 23. The voltage differs in value depending on the gate voltage.

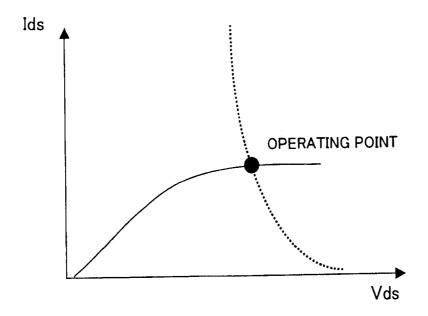

[0038] This TFT 21 is driven in the saturated region, so a current Ids of the value of the above equation 1 is supplied for the Vgs for the source voltage of the operating point. However, here too, similarly, the I-V characteristic of the organic EL element ends up deteriorating along with elapse. As shown in FIG. 6, the operating point ends up fluctuating due

to this deteriorating along with elapse. The source voltage fluctuates even if supplying the same gate voltage.

[0039] Due to this, the gate-source voltage Vgs of the drive transistor constituted by the TFT 21 ends up changing and the value of the current flowing fluctuates. The value of the current flowing through the organic EL element 23 simultaneously changes, so if the I-V characteristic of the organic EL element 23 deteriorates, the luminance of the emitted light will end up changing along with elapse in the source-follower circuit of FIG. 4.

[0040] Further, as shown in FIG. 7, a circuit configuration where the source of the drive transistor constituted by the n-channel TFT 21 is connected to the ground potential GND, the drain is connected to the cathode of the organic EL light emitting element 23, and the anode of the organic EL light emitting element 23 is connected to the power source potential Vcc may be considered.

[0041] With this system, in the same way as when driven by the p-channel TFT of FIG. 2, the potential of the source is fixed, the drive transistor constituted by the TFT 21 operates as a constant current source, and a change in the luminance due to deterioration of the I-V characteristic of the organic EL element can be prevented.

[0042] With this system, however, the drive transistor has to be connected to the cathode side of the organic EL light emitting element. This cathodic connection requires development of new anode-cathode electrodes. This is considered extremely difficult with the current level of technology.

[0043] From the above, in the past systems, no organic EL light emitting element using a n-channel transistor free of change in luminance has been developed.

## DISCLOSURE OF THE INVENTION

[0044] An object of the present invention is to provide a pixel circuit, display device, and method of driving a pixel circuit enabling source-follower output with no deterioration of luminance even with a change of the current-voltage characteristic of the light emitting element along with elapse, enabling a source-follower circuit of n-channel transistors, and able to use an n-channel transistor as an EL element transistor while using current anode-cathode electrodes.

[0045] To achieve the above object, according to a first aspect of the present invention, there is provided a pixel circuit for driving an electro-optic element with a luminance changing according to a flowing current, comprising a data line through which a data signal in accordance with luminance information is supplied; a first control line; first and second nodes; first and second reference potentials; a drive transistor forming a current supply line between the first terminal and the second terminal and controlling a current flowing through the current supply line in accordance with the potential of a control terminal connected to the second node; a pixel capacitance element connected between the first node and the second node; a first switch connected between the data line and either of a first terminal or second terminal of the pixel capacitance element and controlled in conduction by the first control line; and a first circuit for making a potential of the first node change to a fixed potential while the electrooptic element is not emitting light; the current supply line of the drive transistor, the first node, and the electro-optic element being connected in series between the first reference potential and second reference potential.

[0046] Preferably, the circuit further comprises a second control line; the drive transistor is a field effect transistor with

a source connected to the first node, a drain connected to the first reference potential or second reference potential, and a gate connected to the second node; and the first circuit includes a second switch connected between the first node and fixed potential and is controlled in conduction by the second control line.

[0047] Preferably, when the electro-optic element is driven, as a first stage, the first switch is held in a non-conductive state by the first control line, the second switch is held in a conductive state by the second control line, and the first node is connected to a fixed potential; as a second stage, the first switch is held in a conductive state by the first control line, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state; and as a third stage, the second switch is held in a non-conductive state by the second control line.

[0048] Preferably, the circuit further comprises a second control line; the drive transistor is a field effect transistor with a drain connected to the first reference potential or second reference potential and a gate connected to the second node; and the first circuit includes a second switch connected between a source of the field effect transistor and an electro-optic element and is controlled in conduction by the second control line.

[0049] Preferably, when the electro-optic element is driven, as a first stage, the first switch is held in a non-conductive state by the first control line, and the second switch is held in a non-conductive state by the second control line; as a second stage, the first switch is held in a conductive state by the first control line, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state; and as a third stage, the second switch is held in a conductive state by the second control line.

[0050] Preferably, the circuit further comprises a second control line; the drive transistor is a field effect transistor with a source connected to the first node, a drain connected to the first reference potential or second reference potential, and a gate connected to the second node; and the first circuit includes a second switch connected between the first node and the electro-optic element and is controlled in conduction by the second control line.

[0051] Preferably, when the electro-optic element is driven, as a first stage, the first switch is held in a non-conductive state by the first control line, and the second switch is held in a non-conductive state by the second control line; as a second stage, the first switch is held in a conductive state by the first control line, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state; and as a third stage, the second switch is held in a conductive state by the second control line.

[0052] Preferably, the circuit further has a second circuit making the first node be held at a fixed potential when the first switch is held in a conductive state and writes data propagated through the data line.

[0053] Preferably, the circuit further comprises second and third control lines and a voltage supply; the drive transistor is a field effect transistor with a drain connected to the first reference potential or second reference potential and a gate connected to the second node; the first circuit includes a second switch connected between a source of the field effect transistor and the electro-optic element and is controlled in conduction by the second control line; and the second circuit

includes a third switch connected between the first node and the voltage source and is controlled in conduction by the third control line.

[0054] Preferably, when the electro-optic element is driven, as a first stage, the first switch is held in a non-conductive state by the first control line, the second switch is held in a non-conductive state by the second control line, and the third switch is held in a non-conductive state by the third control line; as a second stage, the first switch is held in a conductive state by the first control line, the third switch is held in a conductive state by the third control line, the first node is held at a predetermined potential, and, in that state, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state by the first control line; and as a third stage, the third switch is held in a non-conductive state by the third control line and the second switch is held in a conductive state by the second control line.

[0055] Preferably, the circuit further has second and third control lines and a voltage source; the drive transistor is a field effect transistor with a source connected to the first node, a drain connected to the first reference potential or second reference potential, and a gate connected to the second node; the first circuit includes a second switch connected between the first node and the electro-optic element and controlled in conduction by the second control line; and the second circuit includes a third switch connected between the first node and the voltage source and is controlled in conduction by the third control line.

[0056] Preferably, when the electro-optic element is driven, as a first stage, the first switch is held in a non-conductive state by the first control line, the second switch is held in a non-conductive state by the second control line, and the third switch is held in a non-conductive state by the third control line; as a second stage, the first switch is held in a conductive state by the first control line, the third switch is held in a conductive state by the third control line, the first node is held at a predetermined potential, and, in that state, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state by the first control line; and as a third stage, the third switch is held in a non-conductive state by the third control line and the second switch is held in a conductive state by the second control line.

[0057] Preferably, the circuit further has a second circuit making the second node be held at a fixed potential when the first switch is held in a conductive state and writes data propagated through the data line.

[0058] Further, the fixed potential is the first reference potential or second reference potential.

[0059] Preferably, the circuit further comprises second, third, and fourth control lines; the drive transistor is a field effect transistor with a source connected to the first node, a drain connected to the first reference potential or second reference potential, and a gate connected to the second node; the first circuit includes a second switch connected between the first node and the electro-optic element and is controlled in conduction by the second control line and a third switch connected between a source of the field effect transistor and the first node and is controlled in conduction by the third control line; and the second circuit includes a fourth switch connected between the first node and the fixed potential and is controlled in conduction by the fourth control line.

[0060] Further, preferably when the electro-optic element is driven, as a first stage, the first switch is held in a nonconductive state by the first control line, the second switch is held in a non-conductive state by the second control line, the third switch is held in a non-conductive state by the third control line, and the fourth switch is held in a non-conductive state by the fourth control line; as a second stage, the first switch is held in a conductive state by the first control line, the fourth switch is held in a conductive state by the fourth control line, the second node is held at a fixed potential, and, in that state, data to be propagated over the data line is written in the pixel capacitance element, then the first switch is held in a non-conductive state by the first control line, and the fourth switch is held at a non-conductive state by the fourth control line; and as a third stage, the second switch is held in a conductive state by the second control line and the third switch is held in a conductive state by the third control line.

[0061] According to a second aspect of the present invention, there is provided a display device comprising a plurality of pixel circuits arranged in a matrix; a data line arranged for each column of the matrix array of pixel circuits and through which a data signal in accordance with luminance information is supplied; a first control line arranged for each row of the matrix array of pixel circuits; and first and second reference potentials; each pixel circuit further having an electrooptic element with a luminance changing according to a flowing current, first and second nodes, a drive transistor forming a current supply line between a first terminal and a second terminal and controlling a current flowing through the current supply line in accordance with the potential of a control terminal connected to the second node, a pixel capacitance element connected between the first node and the second node, a first switch connected between the data line and the second node and controlled in conduction by the first control line, and a first circuit for making a potential of the first node change to a fixed potential while the electro-optic element is not emitting light, the current supply line of the drive transistor, the first node, and the electro-optic element being connected in series between the first reference potential and second reference potential.

[0062] According to a third aspect of the present invention, there is provided a method of driving a pixel circuit having an electro-optic element with a luminance changing according to a flowing current; a data line through which a data signal in accordance with luminance information is supplied; first and second nodes; first and second reference potentials; a field effect transistor with a drain connected to the first reference potential or second reference potential, a source connected to the first node, and a gate connected to the second node; a pixel capacitance element connected between the first node and the second node; a first switch connected between the data line and either of a first terminal or a second terminal of the pixel capacitance element; and a first circuit for making a potential of the first node change to a fixed potential; the current supply line of the drive transistor, the first node, and the electro-optic element being connected in series between the first reference potential and second reference potential, comprising steps of making a potential of the first node change to a fixed potential by the first circuit in the state with the first switch held at a non-conductive state, holding the first switch at a conductive state, writing data propagated over the data line in the pixel capacitance element, then holding the first switch in the nonconductive, and stopping the operation for making a potential of the first node of said first circuit change to a fixed potential.

[0063] According to the present invention, since for example the source electrode of a drive transistor is connected to a fixed potential through a switch and there is a pixel capacitor between the gate and source of the drive transistor, the change in luminance due to the change in the I-V characteristic of a light emitting element along with elapse is corrected.

[0064] When the drive transistor is an n-channel transistor, by making the fixed potential a ground potential, the potential applied to the light emitting element is made the ground potential so as to create a non-emitting period of the light emitting element.

**[0065]** Further, by adjusting the off period of the second switch connecting the source electrode and ground potential, the emitting and non-emitting periods of the light emitting element are adjusted for duty driving.

**[0066]** Further, by making the fixed potential close to the ground potential or a potential lower than that or by raising the gate voltage, deterioration of the image quality due to fluctuation in the threshold voltage Vth of the switching transistor connected to the fixed potential is suppressed.

[0067] Further, when the drive transistor is a p-channel transistor, by making the fixed potential the potential of the power source connected to the cathode electrode of the light emitting element, the potential applied to the light emitting element is made the power source potential so as to create a non-emitting period of the EL element.

[0068] Further, by making the characteristic of the drive transistor an n-channel type, a source-follower circuit becomes possible and anodic connection becomes possible.

[0069] Further, making all of the drive transistors n-channel transistors becomes possible, introduction of a general amorphous silicon process becomes possible, and reduction of the cost becomes possible.

[0070] Further, since the second switching transistor is laid out between the light emitting element and the drive transistor, current is not supplied to the drive transistor in the non-emitting period and therefore power consumption of the panel is suppressed.

[0071] Further, by using a potential of the cathode side of the light emitting element as the ground potential, for example, the second reference potential, there is no need to provide a GND line at the TFT side inside the panel.

**[0072]** Further, by being able to delete the GND lines of the TFT boards in the panel, layout in the pixels and layout of the peripheral circuits become easy.

[0073] Further, by being able to delete the GND lines of the TFT boards in the panel, there is no overlap between the power source potential (first reference potential) and ground potential (second reference potential) of the peripheral circuits, the Vcc lines can be laid out with a lower resistance, and a high uniformity can be achieved.

[0074] Further, by connecting for example a pixel capacitance element to the source of a drive transistor and boosting one side of the capacitor to the power source while not emitting light, there is no longer a need for a GND line at the TFT side at the inside of the panel.

[0075] Further, by turning the fourth switch at the power source line side on when writing in a signal line so as to lower the impedance, the coupling effect on pixel writing is corrected in a short time and an image of a high uniformity is obtained.

[0076] Further, by making the potential of the power source line the same as the Vcc potential, it is possible to reduce the panel lines.

[0077] Further, according to the present invention, by connecting the gate electrode of the drive transistor to a fixed potential through a switch and providing a pixel capacitor between the gate and source of the drive transistor, change of the luminance due to deterioration of the I-V characteristic of the light emitting element along with elapse is corrected.

[0078] For example, when the drive transistor is an rechannel, by making the fixed potential the fixed potential to which the drain electrode of the drive transistor is connected, the fixed potential is made only the power source potential in the pixel.

[0079] Further, by raising the gate voltages of the switching transistors connected to the gate side and source side of the drive transistor or making the transistors larger in size, deterioration of the image quality due to variation in the threshold values of the switching transistors is suppressed. Further, when the drive transistor is a p-channel, by making the fixed potential the fixed potential to which the drain electrode of the driven is connected, the fixed potential is made only GND in the pixel.

[0080] Further, by raising the gate voltages of the switching transistors connected to the gate side and source side of the drive transistor or making the transistors larger in size, deterioration of the image quality due to variation in the threshold values of the switching transistors is suppressed.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0081] FIG. 1 is a block diagram of the configuration of a general organic EL display device.

[0082] FIG. 2 is a circuit diagram of an example of the configuration of a pixel circuit of FIG. 1.

[0083] FIG. 3 is a graph of the change along with elapse of the current-voltage (I-V) characteristic of an organic EL device.

[0084] FIG. 4 is a circuit diagram of a pixel circuit in which p-channel TFTs of the circuit of FIG. 2 are replaced by n-channel TFTs.

[0085] FIG. 5 is a graph showing the operating point of a drive transistor constituted by a TFT and an EL light emitting element in the initial state.

[0086] FIG. 6 is a graph showing the operating point of a drive transistor constituted by a TFT and an EL light emitting element after change along with elapse.

[0087] FIG. 7 is a circuit diagram of a pixel circuit connecting a source of a drive transistor constituted by an n-channel TFT to a ground potential.

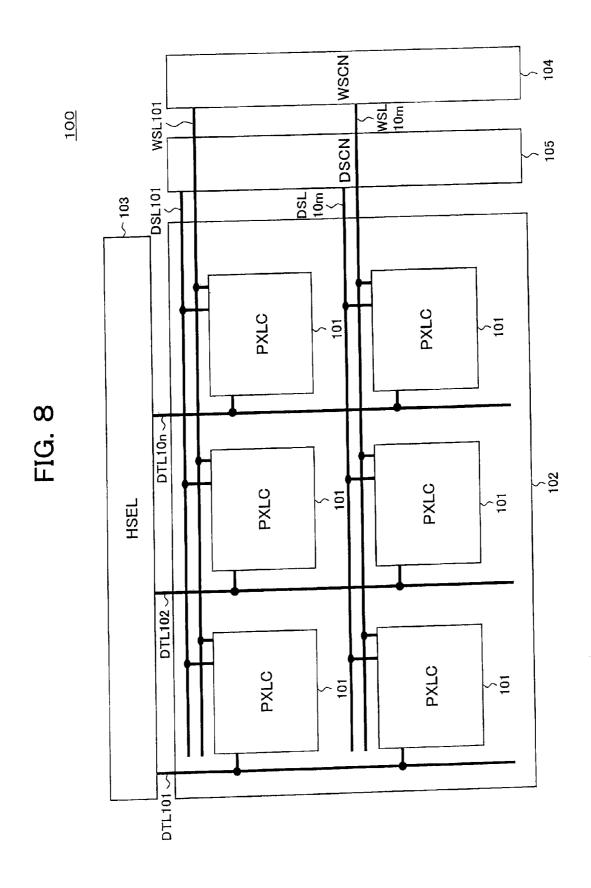

[0088] FIG. 8 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a first embodiment.

[0089] FIG. 9 is a circuit diagram of a specific configuration of a pixel circuit according to the first embodiment in the organic EL display device of FIG. 1.

[0090] FIGS. 10A to 10F are views of equivalent circuits for explaining the operation of the circuit of FIG. 9.

[0091] FIGS. 11A to 11F are timing charts for explaining the operation of the circuit of FIG. 9.

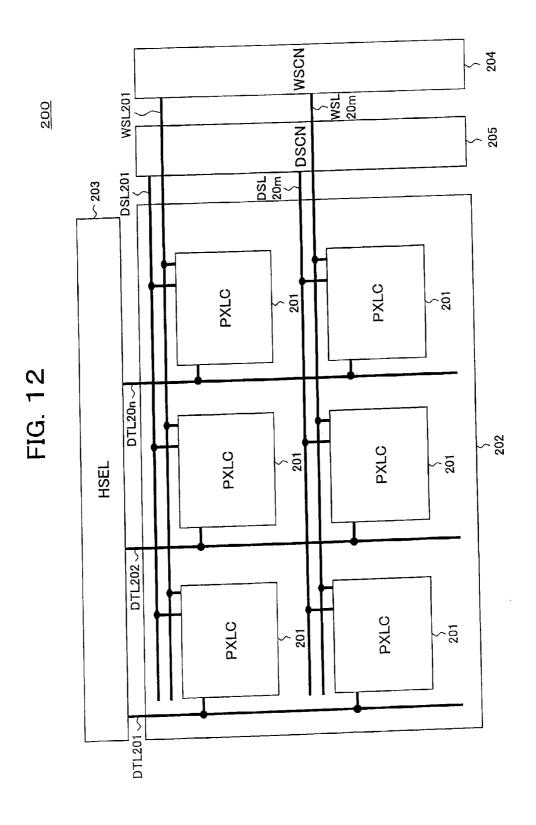

[0092] FIG. 12 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a second embodiment.

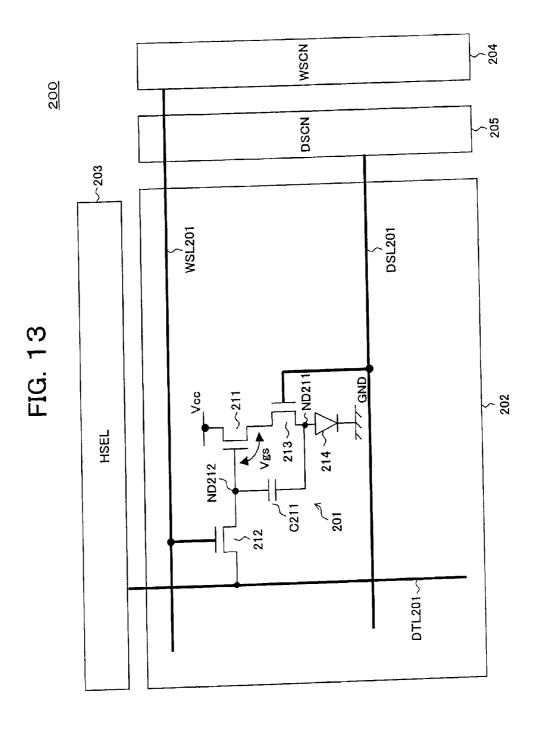

[0093] FIG. 13 is a circuit diagram of a specific configuration of a pixel circuit according to the second embodiment in the organic EL display device of FIG. 12.

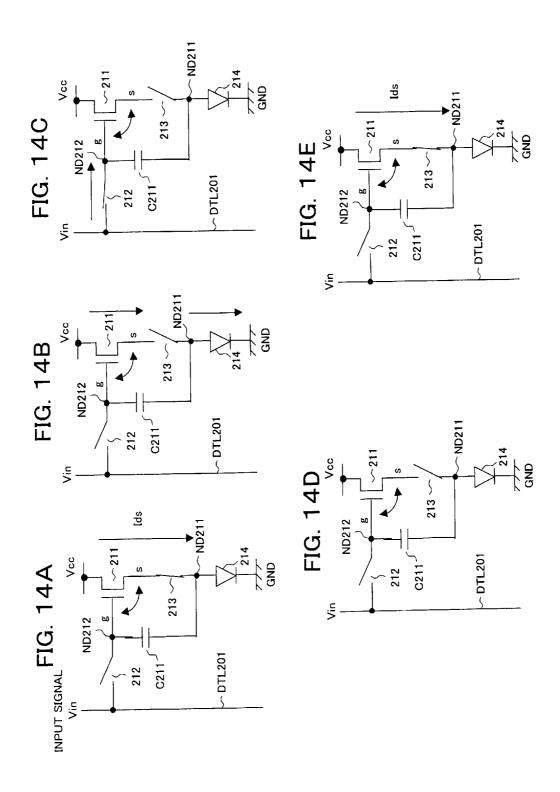

[0094] FIGS. 14A to 14E are views of equivalent circuits for explaining the operation of the circuit of FIG. 13.

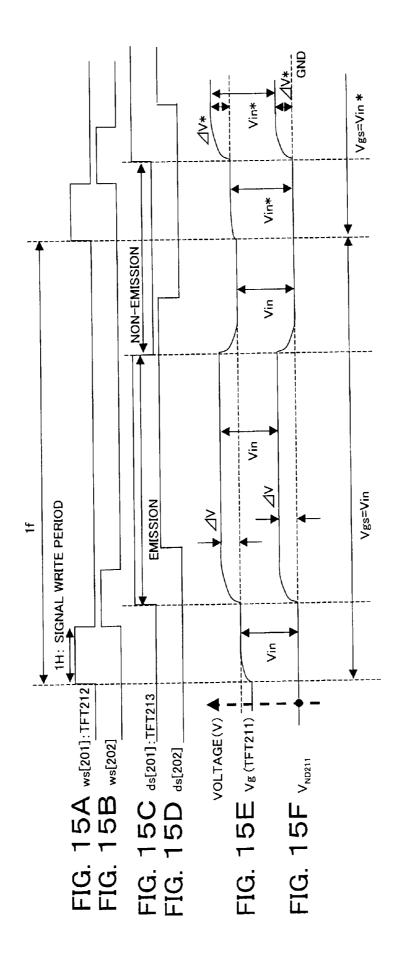

[0095] FIGS. 15A to 15F are timing charts for explaining the operation of the circuit of FIG. 13.

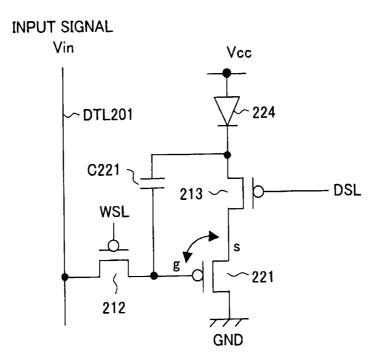

[0096] FIG. 16 is a circuit diagram of another example of the configuration of a pixel circuit according to the second embodiment.

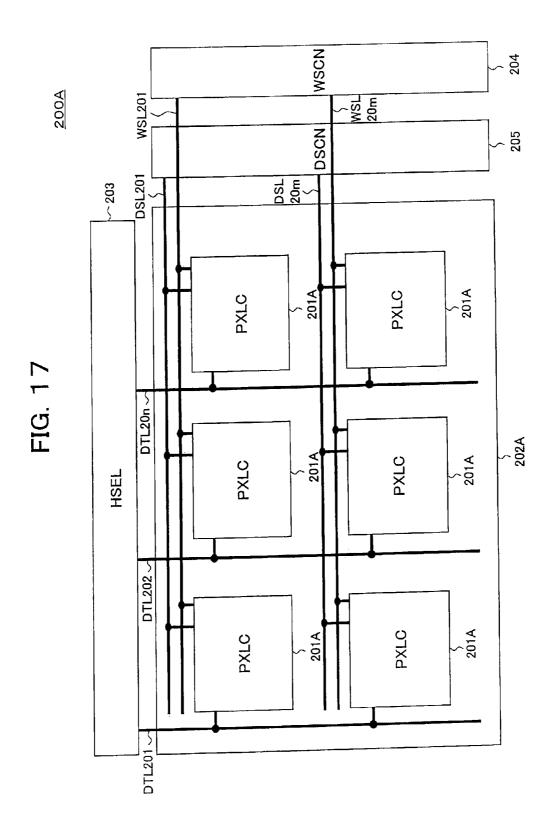

[0097] FIG. 17 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a third embodiment.

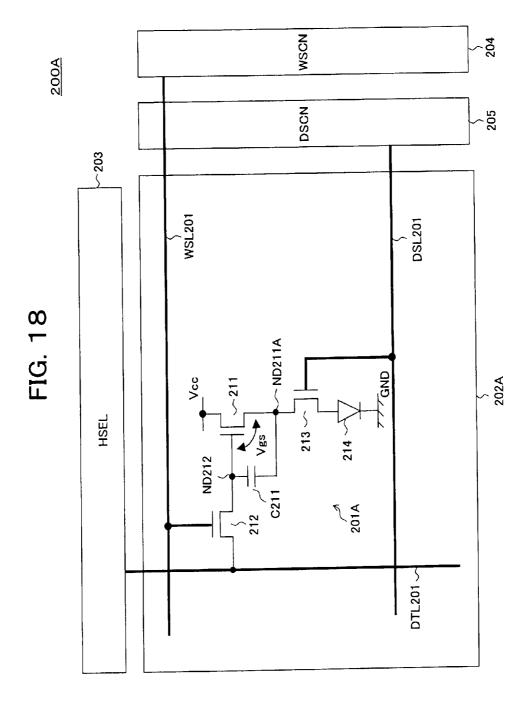

[0098] FIG. 18 is a circuit diagram of a specific configuration of a pixel circuit according to the third embodiment in the organic EL display device of FIG. 17.

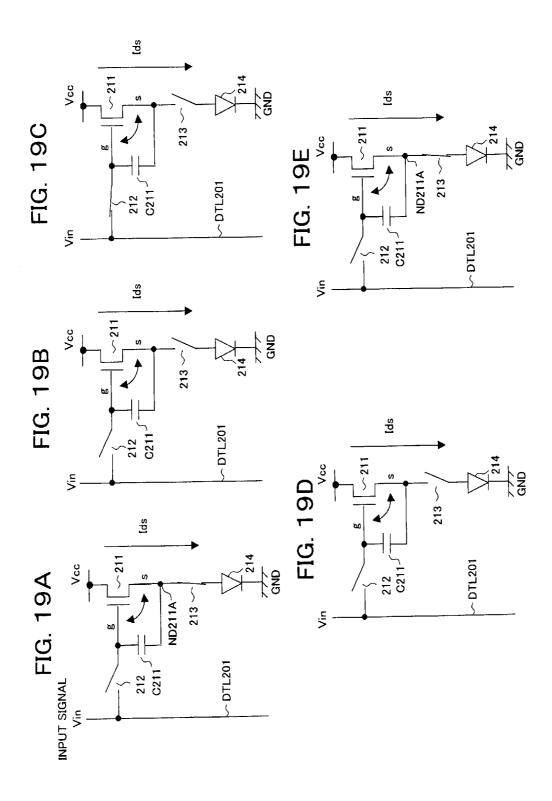

[0099] FIGS. 19A to 19E are views of equivalent circuits for explaining the operation of the circuit of FIG. 18.

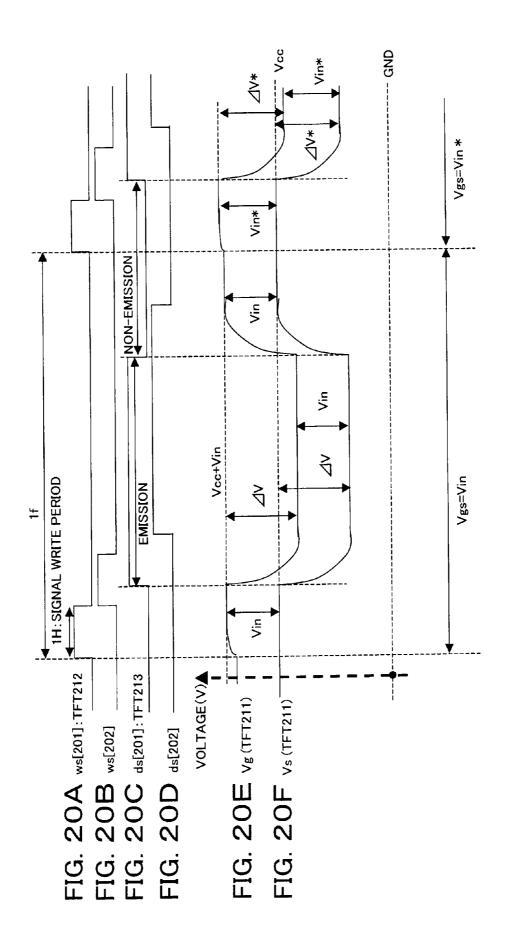

[0100] FIGS. 20A to 20F are timing charts for explaining the operation of the circuit of FIG. 18.

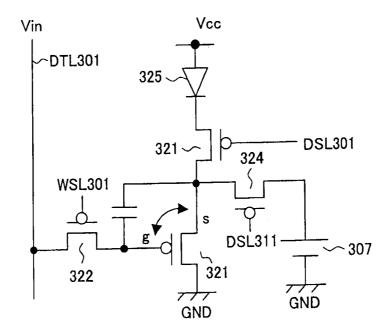

[0101] FIG. 21 is a circuit diagram of another example of the configuration of a pixel circuit according to the third embodiment.

[0102] FIG. 22 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a fourth embodiment.

[0103] FIG. 23 is a circuit diagram of a specific configuration of a pixel circuit according to the fourth embodiment in the organic EL display device of FIG. 22.

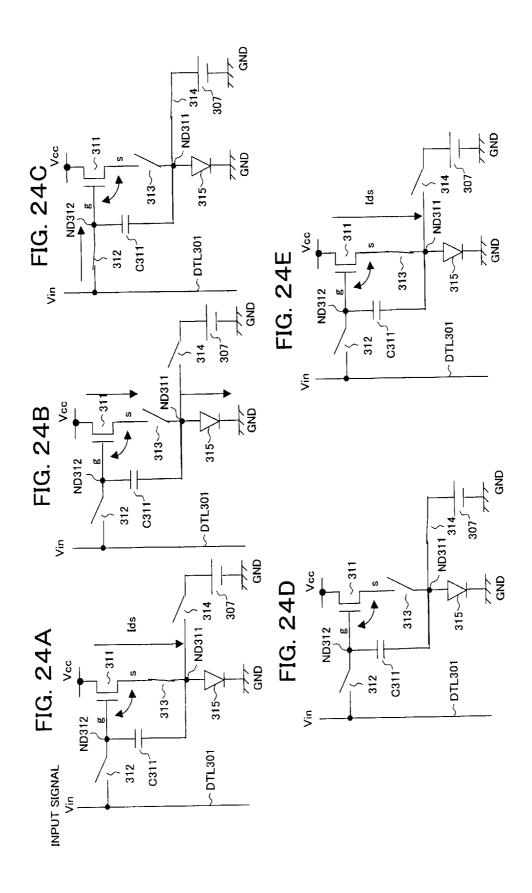

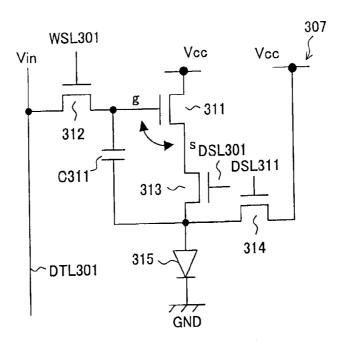

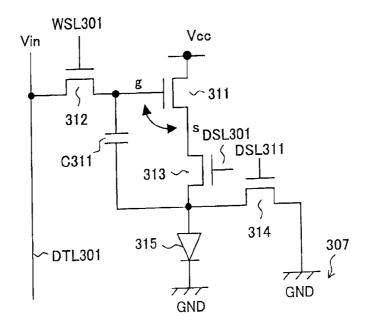

[0104] FIGS. 24A to 24E are views of equivalent circuits for explaining the operation of the circuit of FIG. 23.

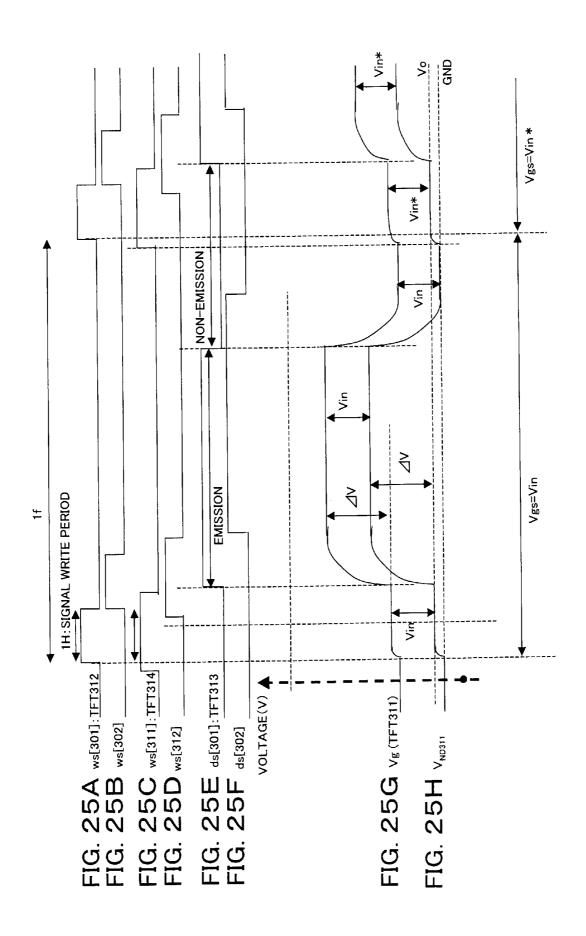

[0105] FIGS. 25A to 25H are timing charts for explaining the operation of the circuit of FIG. 23.

[0106] FIG. 26 is a circuit diagram of a pixel circuit having a fixed voltage line as the power source potential VCC.

[0107] FIG. 27 is a circuit diagram of a pixel circuit having a fixed voltage line as the ground potential GND.

[0108] FIG. 28 is a circuit diagram of another example of the configuration of a pixel circuit according to the fourth embodiment

[0109] FIG. 29 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a fifth embodiment.

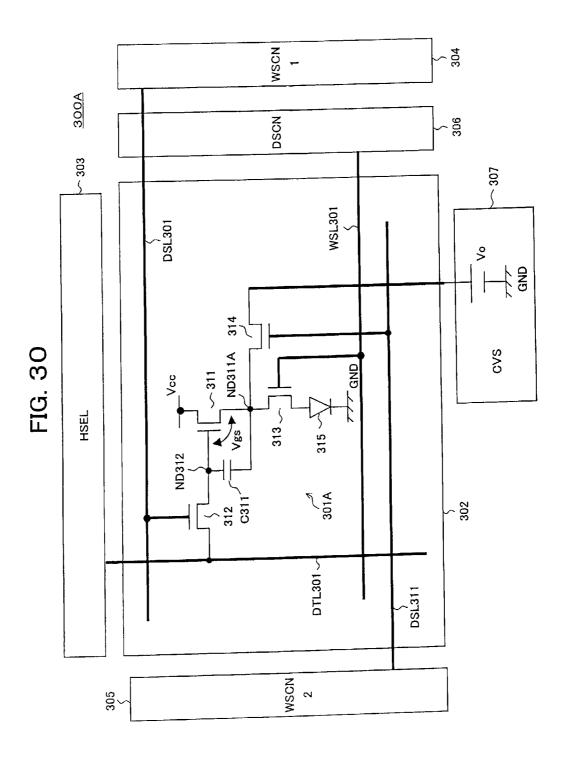

[0110] FIG. 30 is a circuit diagram of a specific configuration of a pixel circuit according to the fifth embodiment in the organic EL display device of FIG. 29.

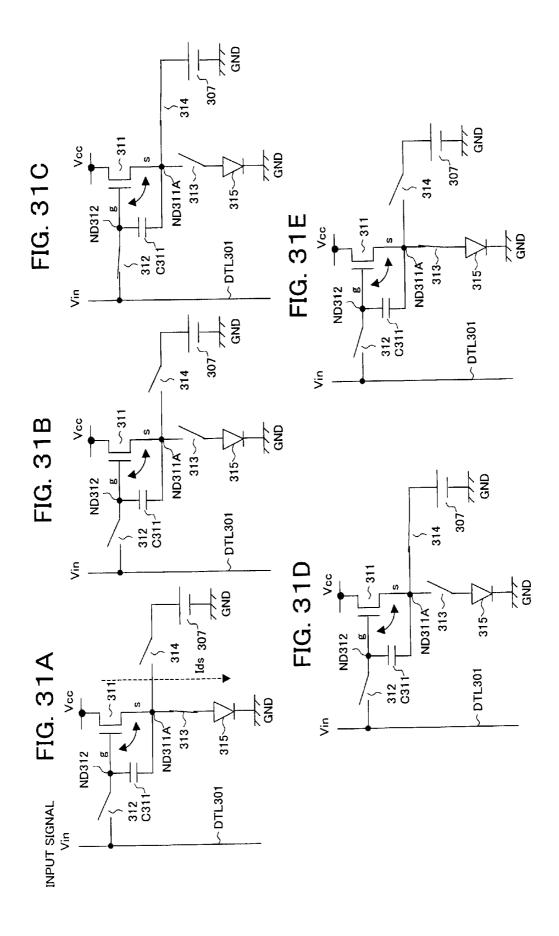

[0111] FIGS. 31A to 31E are views of equivalent circuits for explaining the operation of the circuit of FIG. 30.

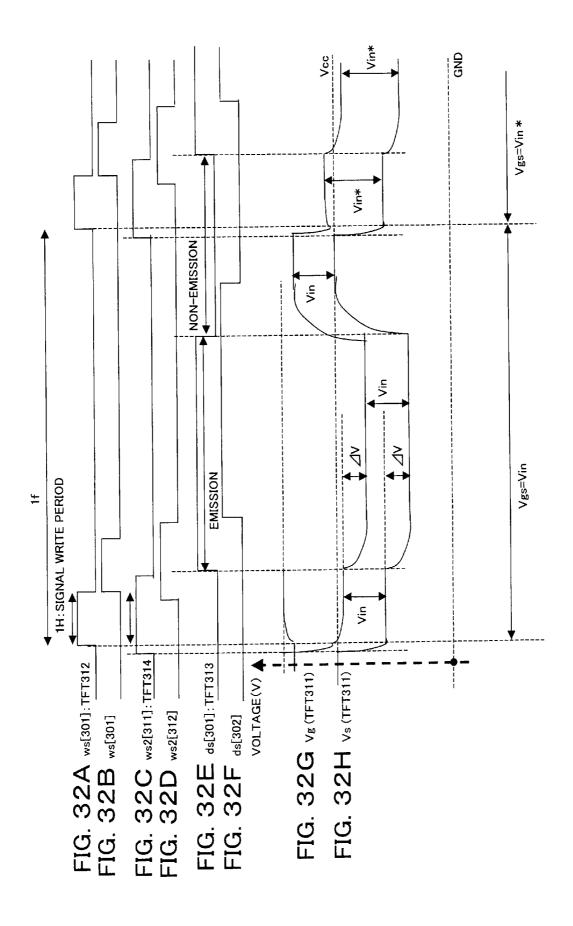

[0112] FIGS. 32A to 32H are timing charts for explaining the operation of the circuit of FIG. 30.

[0113] FIG. 33 is a circuit diagram of a pixel circuit having a fixed voltage line as the power source potential VCC.

[0114] FIG. 34 is a circuit diagram of a pixel circuit having a fixed voltage line as the ground potential GND.

[0115] FIG. 35 is a circuit diagram of another example of the configuration of a pixel circuit according to the fifth embodiment.

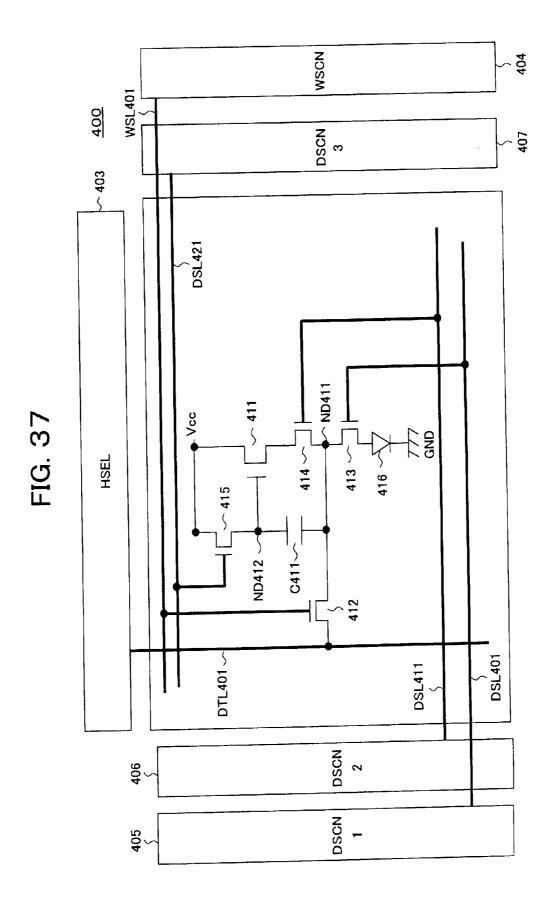

[0116] FIG. 36 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a sixth embodiment.

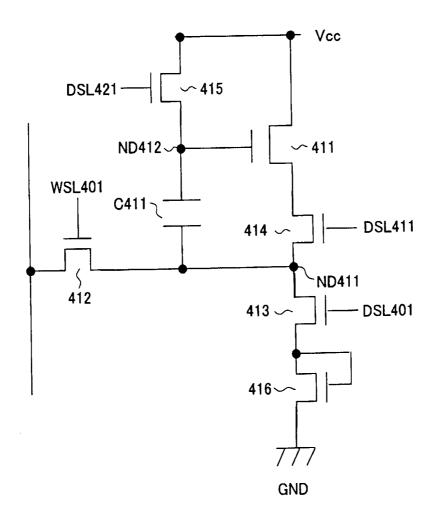

[0117] FIG. 37 is a circuit diagram of a specific configuration of a pixel circuit according to the sixth embodiment in the organic EL display device of FIG. 36.

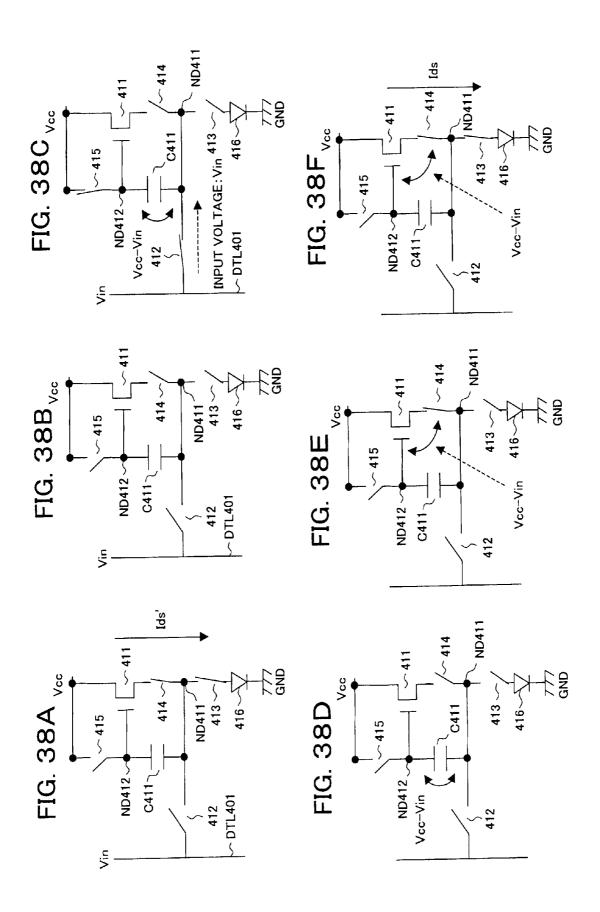

[0118] FIGS. 38A to 38F are views of equivalent circuits for explaining the operation of the circuit of FIG. 37.

[0119] FIG. 39 is a view of an equivalent circuit for explaining the operation of the circuit of FIG. 37.

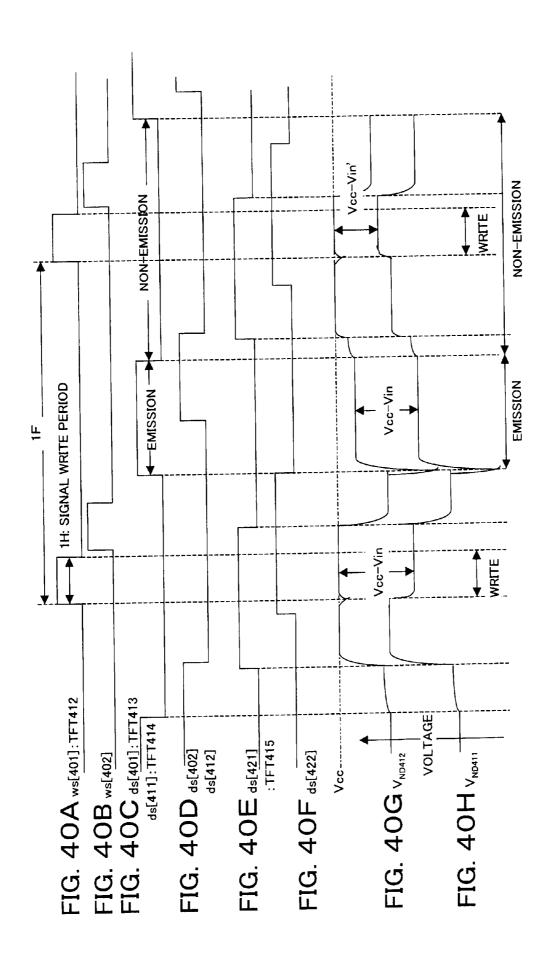

[0120] FIGS. 40A to 40H are timing charts for explaining the operation of the circuit of FIG. 37.

## BEST MODE FOR WORKING THE INVENTION

[0121] Below, preferred embodiments of the present invention will be described with reference to the accompanying drawings.

## First Embodiment

[0122] FIG. 8 is a block diagram of the configuration of an organic EL display device employing pixel circuits according to the first embodiment.

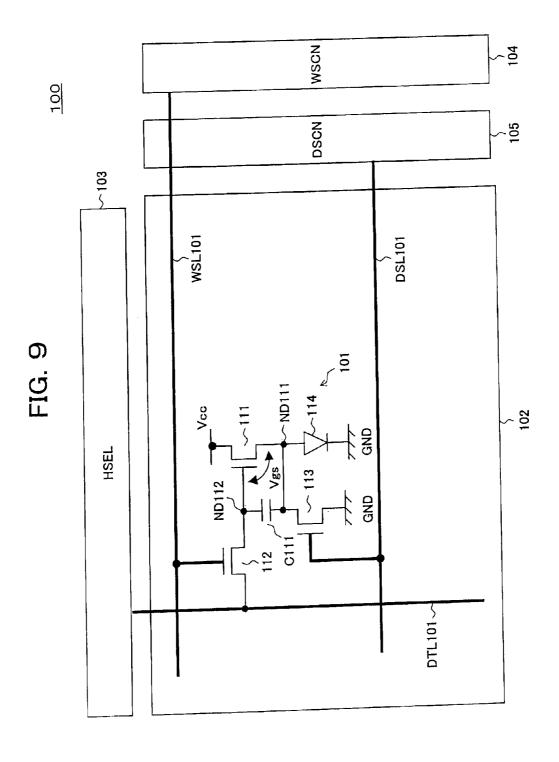

[0123] FIG. 9 is a circuit diagram of the concrete configuration of a pixel circuit according to the first embodiment in the organic EL display device of FIG. 8.

[0124] This display device 100 has, as shown in FIG. 8 and FIG. 9, a pixel array portion 102 having pixel circuits (PXLC) 101 arranged in an m×n matrix, a horizontal selector (HSEL) 103, a write scanner (WSCN) 104, a drive scanner (DSCN) 105, data lines DTL101 to DTL10n selected by the horizontal selector 103 and supplied with a data signal in accordance with the luminance information, scanning lines WSL101 to WSL10m selectively driven by the write scanner 104, and drive lines DSL101 to DSL10m selectively driven by the drive scanner 105.

[0125] Note that while the pixel circuits 101 are arranged in an  $m \times n$  matrix in the pixel array portion 102, FIG. 9 shows an example wherein the pixel circuits are arranged in a 2 (=m)×3 (=n) matrix for the simplification of the drawing.

[0126] Further, in FIG. 9, the concrete configuration of one pixel circuit is shown for simplification of the drawing.

[0127] The pixel circuit 101 according to the first embodiment has, as shown in FIG. 9, an n-channel TFT 111 to TFT 113, a capacitor C111, a light emitting element 114 made of an organic EL element (OLED), and nodes ND111 and ND112.

[0128] Further, in FIG. 9, DTL101 indicates a data line, WSL101 indicates a scanning line, and DSL101 indicates a drive line

[0129] Among these components, TFT 111 configures the field effect transistor according to the present invention, TFT 112 configures the first switch, TFT 113 configures the second switch, and the capacitor C111 configures the pixel capacitance element according to the present invention.

[0130] Further, the scanning line WSL101 corresponds to the first control line according to the present invention, while the drive line DSL101 corresponds to the second control line.

[0131] Further, the supply line (power source potential) of the power source voltage Vcc corresponds to the first reference potential, while the ground potential GND corresponds to the second reference potential.

[0132] In the pixel circuit 101, a light emitting element (OLED) 114 is connected between a source of the TFT 111 and the second reference potential (in this present embodiment, the ground potential GND). Specifically, the anode of the light emitting element 114 is connected to the source of the TFT 111, while the cathode side is connected to the

ground potential GND. The connection point of the anode of the light emitting element 114 and the source of the TFT 111 constitutes a node ND111.

[0133] The source of the TFT 111 is connected to a drain of the TFT 113 and a first electrode of the capacitor C111, while the gate of the TFT 111 is connected to a node ND112.

[0134] The source of the TFT 113 is connected to a fixed potential (in the present embodiment, a ground potential GND), while the gate of the TFT 113 is connected to the drive line DSL101. Further, a second electrode of the capacitor C111 is connected to the node ND112.

[0135] A source and a drain of the TFT 112 as first switch are connected to the data line DTL101 and node ND112. Further, a gate of the TFT 112 is connected to the scanning line WSL101.

[0136] In this way, the pixel circuit 101 according to the present embodiment is configured with a capacitor C111 connected between the gate and source of the TFT 111 as the drive transistor and with a source potential of the TFT 111 connected to a fixed potential through the TFT 113 as the switching transistor.

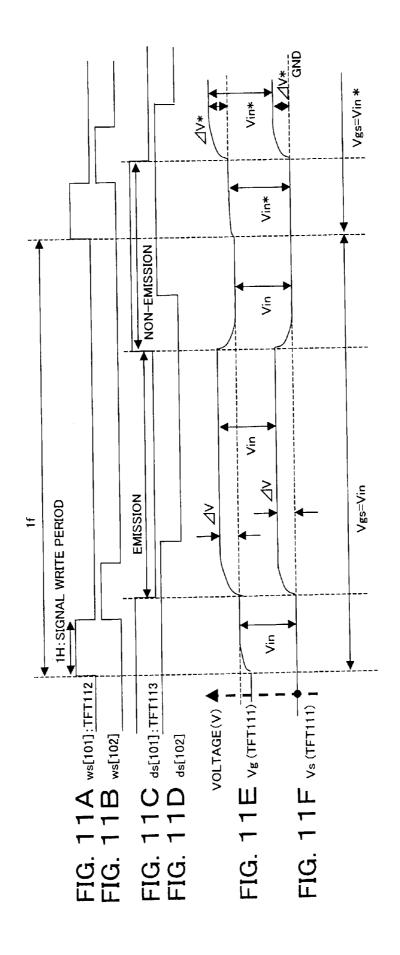

[0137] Next, the operation of the above configuration will be explained focusing on the operation of a pixel circuit with reference to FIGS. 10A to 10F and FIGS. 11A to 11F.

[0138] Note that FIG. 11A shows a scanning signal ws[101] applied to the first row scanning line WSL101 of the pixel array, FIG. 11B shows a scanning signal ws[102] applied to the second row scanning line WSL102 of the pixel array, FIG. 11C shows a drive signal ds[101] applied to the first row drive line DSL101 of the pixel array, FIG. 11D shows a drive signal ds[101] applied to the second row drive line DSL102 of the pixel array, FIG. 11E shows a gate potential Vg of the TFT 111, and FIG. 11F shows a source potential Vs of the TFT 111.

[0139] First, at the time of the ordinary emitting state of the EL light emitting element 114, as shown in FIGS. 11A to 11D, the scanning signals ws[101], ws[102], . . . to the scanning lines WSL101, WSL102, . . . are selectively set to the low level by the write scanner 104, and the drive signals ds[101], ds[102], . . . to the drive lines DSL101, DSL102, . . . are selectively set to the low level by the drive scanner 105.

[0140] As a result, in the pixel circuits 101, as shown in FIG. 10A, the TFT 112 and TFT 113 are held in the off state. [0141] Next, in the non-emitting period of the EL element 114, as shown in FIGS. 11A to 11D, the scanning signals ws[101], ws[102], . . . to the scanning lines WSL101, WSL102, . . . are held at the low level by the write scanner 104, and the drive signals ds[101], ds[102], . . . to the drive lines DSL101, DSL102, . . . are selectively set to the high level by the drive scanner 105.

[0142] As a result, in the pixel circuits 101, as shown in FIG. 10B, the TFT 112 is held in the off state and the TFT 113 is turned off.

[0143] At this time, current flows through the TFT 113 and, as shown in FIG. 11F, the source potential Vs of the TFT 111 falls to the ground potential GND. Therefore, the voltage applied to the EL light emitting element 114 also becomes 0V and the EL light emitting element 114 becomes non-emitting in state.

[0144] Next, in the non-emitting period of the EL light emitting element 114, as shown in FIGS. 11A to 11D, the drive signals ds[101], ds[102],... to the drive lines DSL101, DSL102,... are held at the high level by the drive scanner 105, and the scanning signals ws[101], ws[102],... to the

scanning lines WSL101, WSL102, . . . are selectively set to the high level by the write scanner 104.

[0145] As a result, in the pixel circuits 101, as shown in FIG. 10C, the TFT 113 is held in the on state and the TFT 112 is turned on. Due to this, the horizontal selector 103 writes the input signal (Vin) propagated to the data line DTL101 into the capacitor C111 as the pixel capacitor.

[0146] At this time, as shown in FIG. 11F, the source potential Vs of the TFT 111 as the drive transistor is at the ground potential level (GND level), so, as shown in FIGS. 11E and 11F, the potential difference between the gate and source of the TFT 111 becomes equal to the voltage Vin of the input signal.

[0147] After this, in the non-emitting period of the EL light emitting element 114, as shown in FIGS. 11A to 11D, the drive signals ds[101], ds[102],... to the drive lines DSL101, DSL102,... are held at the high level by the drive scanner 105 and the scanning signals ws[101], ws[102],... to the scanning lines WSL101, WSL102,... are selectively set to the low level by the write scanner 104.

[0148] As a result, in the pixel circuit 101, as shown in FIG. 10D, the TFT 112 is turned off and the write operation of the input signal to the capacitor C111 as the pixel capacitor ends. [0149] After this, as shown in FIGS. 11A to 11D, the scanning signals ws[101], ws[102], . . . to the scanning lines WSL101, WSL102, . . . are held at the low level by the write scanner 104 and the drive signals ds[101], ds[102], . . . to the drive lines DSL101, DSL102, . . . are selectively set to the low level by the drive scanner 104.

[0150] As a result, in the pixel circuit 101, as shown in FIG. 10E, the TFT 113 is turned off.

[0151] By turning the TFT 113 off, as shown in FIG. 11F, the source potential Vs of the TFT 111 as the drive transistor rises and current also flows to the EL light emitting element 114.

[0152] The source potential Vs of the TFT 111 fluctuates, but despite this, since there is a capacitor between the gate and source of the TFT 111, as shown in FIGS. 11E and 11F, the gate-source potential is constantly held at Vin.

[0153] At this time, the TFT 111 as the drive transistor drives in the saturated region, so the current Ids flowing through the TFT 111 becomes the value shown in the above equation 1. This value is determined by the gate source potential Vin of the TFT 111. This current Ids similarly flows to the EL light emitting element 114, whereby the EL light emitting element 114 emits light.

[0154] The equivalent circuit of the EL light emitting element 114 becomes as shown in FIG. 10F, so at this time the potential of the node ND111 rises to the gate potential by which the current Ids flows through the EL light emitting element 114.

[0155] Along with this rise in potential, the potential of the node ND112 also similarly rises through the capacitor 111 (pixel capacitor Cs). Due to this, as explained above, the gate-source potential of the TFT 111 is held at Vin.

[0156] Here, consider the problems in the past source-follower system in the circuit of the present invention. In this circuit as well, the EL light emitting element deteriorates in its I-V characteristic along with the increase in the emitting period. Therefore, even if the drive transistor sends the same current, the potential applied to the EL light emitting element changes and the potential of the node ND111 falls.

[0157] However, in this circuit, the potential of the node ND111 falls while the gate-source potential of the drive tran-

sistor is held constant, so the current flowing through the drive transistor (TFT 111) does not change. Accordingly, the current flowing through the EL light emitting element also does not change. Even if the I-V characteristic of the EL light emitting element deteriorates, a current corresponding to the input voltage Vin constantly flows. Therefore, the past problem can be solved.

[0158] As explained above, according to the present first embodiment, the source of the TFT 111 as the drive transistor is connected to the anode of the light emitting element 114, the drain is connected to the power source potential Vcc, a capacitor C111 is connected between the gate and source of the TFT 111, and the source potential of the TFT 111 is connected to a fixed potential through the TFT 113 as the switching transistor, so the following effects can be obtained. [0159] Source-follower output with no deterioration in luminance even with a change in the I-V characteristic of an EL light emitting element along with elapse becomes possible.

[0160] A source-follower circuit of n-channel transistors becomes possible, so it is possible to use an n-channel transistor as a drive element of an EL light emitting element while using current anode-cathode electrodes.

**[0161]** Further, it is possible to configure transistors of a pixel circuit by only n-channel transistors and possible to use the a-Si process in the fabrication of the TFTs. Due to this, there is the advantage that a reduction of the cost of TFT boards becomes possible.

## Second Embodiment

[0162] FIG. 12 is a block diagram of the configuration of an organic EL display device employing pixel circuits according to a second embodiment.

[0163] FIG. 13 is a circuit diagram of the concrete configuration of a pixel circuit according to the second embodiment in the organic EL display device of FIG. 12.

[0164] The display device 200, as shown in FIG. 12 and FIG. 13, has a pixel array portion 202 having pixel circuits (PXLC) 201 arranged in an m×n matrix, a horizontal selector (HSEL) 203, a write scanner (WSCN) 204, a drive scanner (DSCN) 205, data lines DTL201 to DTL20n selected by the horizontal selector 203 and supplied with a data signal in accordance with the luminance information, scanning lines WSL201 to WSL20m selectively driven by the write scanner 204, and drive lines DSL201 to DSL20m selectively driven by the drive scanner 205.

[0165] Note that while the pixel circuits 201 are arranged in an  $m \times n$  matrix in the pixel array portion 202, FIG. 12 shows an example wherein the pixel circuits are arranged in a 2 (=m)×3 (=n) matrix for the simplification of the drawing.

[0166] Further, in FIG. 13 as well, the concrete configuration of one pixel circuit is shown for simplification of the drawing.

[0167] Each pixel circuit 201 according to the second embodiment has, as shown in FIG. 13, an n-channel TFT 211 to TFT 213, a capacitor C211, a light emitting element 214 made of an organic EL element (OLED), and nodes ND211 and ND212.

[0168] Further, in FIG. 13, DTL201 indicates a data line, WSL201 indicates a scanning line, and DSL201 indicates a drive line.

[0169] Among these components, the TFT 211 configures the field effect transistor according to the present invention, the TFT 212 configures the first switch, the TFT 213 config-

ures the second switch, and the capacitor C211 configures the pixel capacitance element according to the present invention. [0170] Further, the scanning line WSL 201 corresponds to the first control line according to the present invention, while the drive line DSL201 corresponds to the second control line. [0171] Further, the supply line of the power source voltage Vcc (power source potential) corresponds to the first reference potential, while the ground potential GND corresponds to the reference potential.

[0172] In each pixel circuit 201, a source and a drain of the TFT 213 are connected between a source of the TFT 211 and an anode of the light emitting element 214, a drain of the TFT 211 is connected to the power source potential Vcc, and a cathode of the light emitting element 214 is connected to the ground potential GND. That is, the TFT 211 as the drive transistor, the TFT 213 as the switching transistor, and the light emitting element 214 are connected in series between the power source potential Vcc and the ground potential GND. Further, the connection point of the anode of the light emitting element 214 and the source of the TFT 213 constitutes a node ND211.

[0173] A gate of the TFT 211 is connected to the node ND212. Further, the capacitor C211 as a pixel capacitor Cs connected between the nodes ND211 and ND212, that is, between the gate of the TFT 211 and the anode of the light emitting element 214. A first electrode of the capacitor C211 is connected to the node ND211, while a second electrode is connected to the node ND212.

[0174] A gate of the TFT 213 is connected to the drive line DSL201. Further, a source and a drain of the TFT 212 as the first switch are connected to the data line DTL201 and the node ND212. Further, a gate of the TFT 212 is connected to the scanning line WSL201.

[0175] In this way, the pixel circuit 201 according to the present embodiment is configured with the source of the TFT 211 as the drive transistor and the anode of the light emitting element 214 connected by the TFT 213 as the switching transistor, while a capacitor C211 connected between the gate of the TFT 211 and the anode of the light emitting element 214.

[0176] Next, the operation of the above configuration will be explained focusing on the operation of a pixel circuit with reference to FIGS. 14A to 14E and FIGS. 15A to 15F.

[0177] Note that FIG. 15A shows a scanning signal ws[201] applied to the first row scanning line WSL201 of the pixel array, FIG. 15B shows a scanning signal ws[202] applied to the second row scanning line WSL202 of the pixel array, FIG. 15C shows a drive signal ds[201] applied to the first row drive line DSL201 of the pixel array, FIG. 15D shows a drive signal ds[202] applied to the second row drivd line DSL202 of the pixel array, FIG. 15E shows a gate potential Vg of the TFT 211, and FIG. 15F shows an anode side potential of the TFT 211, that is, the potential VND211 of the node ND211.

[0178] First, at the ordinary emitting state of the EL light emitting element 214, as shown in FIGS. 15A to 15D, the scanning signals ws[201], ws[202], ... to the scanning lines WSL201, WSL202, ... are selectively set to the low level by the write scanner 204, and the drive signals ds[201], ds[202], ... to the drive lines DSL201, DSL202, ... are selectively set to the high level by the drive scanner 205.

[0179] As a result, in the pixel circuit 201, as shown in FIG. 14A, the TFT 212 is held in the off state and the TFT 213 is held in the on state.

[0180] At this time, the current Ids flows to the TFT 211 as the drive transistor and the EL light emitting element 214.

[0181] Next, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 15A to 15D, the scanning signals ws[201], ws[202], . . . to the scanning lines WSL201, WSL202, . . . are held at the low level by the write scanner 204, and the drive signals ds[201], ds[202], . . . to the drive lines DSL201, DSL202, . . . are selectively set to the low level by the drive scanner 205.

[0182] As a result, in the pixel circuit 201, as shown in FIG. 14B, the TFT 212 is held in the off state and the TFT 213 is turned off.

[0183] At this time, the potential held at the EL light emitting element 214 falls since the source of supply disappears. The potential falls to the threshold voltage Vth of the EL light emitting element 214. However, since current also flows to the EL light emitting element 214, if the non-emitting period continues, the potential will fall to GND.

[0184] On the other hand, the TFT 211 as thr drive transistor is held in the on state since the gate potential is high. This boosting is performed in a short period. After boosting to the Vcc, no current is supplied to the TFT 211.

[0185] That is, in the pixel circuit 201 of the second embodiment, it is possible to operate without the supply of current in the pixel circuit during the non-emitting period and therefore possible to suppress the power consumption of the panel.

[0186] Next, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 15A to 15D, the drive signals ds[201], ds[202], ... to the drive lines DSL201, DSL202, ... are held at the low level by the drive scanner 205, and the scanning signals ws[201], ws[202], ... to the scanning lines WSL201, WSL202, ... are selectively set to the high level by the write scanner 204.

[0187] As a result, in the pixel circuit 201, as shown in FIG. 14C, the TFT 213 is held in the off state and the TFT 212 is turned on. Due to this, the input signal (Vin) propagated to the data line DTL201 by the horizontal selector 203 is written into the capacitor C211 as the pixel capacitor Cs.

[0188] At this time, as shown in FIG. 15F, since the anode side potential Va of the TFT 213 as the switching transistor, that is, the potential VND211 of the node ND211, is at the ground potential level (GND level), the capacitor C211 as the pixel capacitor Cs is held at a potential equal to the voltage Vin of the input signal.

[0189] After this, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 15A to 15D, the drive signals ds[201], ds[202], . . . to the drive lines DSL201, DSL202, . . . are held at the low level by the drive scanner 205, and the scanning signals ws[201], ws[202], . . . to the scanning lines WSL201, WSL202, . . . are selectively set to the low level by the write scanner 204.

[0190] As a result, in the pixel circuit 201, as shown in FIG. 14D, the TFT 212 is turned off and the write operation of the input signal to the capacitor C211 as the pixel capacitor ends. [0191] After this, as shown in FIGS. 15A to 15D, the scanning signals ws[201], ws[202], . . . to the scanning lines WSL201, WSL202, . . . are held at the low level by the write scanner 204, and the drive signals ds[201], ds[202], . . . to the drive lines DSL201, DSL202, . . . are selectively set to the high level by the drive scanner 205.

[0192] As a result, in the pixel circuit 201, as shown in FIG. 14E, the TFT 213 is turned on.

[0193] By turning the TFT 213 on, current flows to the EL light emitting element 214 and the source potential of the TFT 211 falls. The source potential of the TFT 211 as the drive transistor fluctuates, but despite this, since there is a capacitor between the gate of the TFT 211 and the anode of the light emitting element 214, the gate-source potential is held at Vin. At this time, the TFT 211 as the drive transistor is driven in the saturated region, so the current Ids flowing through the TFT 211 becomes the value shown in the above equation 1. This is the gate-source voltage Vgs of the drive transistor.

[0194] Here, the TFT 213 operates in the nonsaturated region, so this is viewed as a simple resistance value. Accordingly, the gate-source voltage of the TFT 211 is Vin minus the value of the voltage drop due to the TFT 211. That is, the current flowing through the TFT 211 can be said to be determined by the Vin.

[0195] Due to the above, even if the EL light emitting element 214 deteriorates in its I-V characteristic along with the increase in the emitting period, in the pixel circuit 201 of the second embodiment, the potential of the node ND211 falls while the potential between the gate and source of the TFT 211 as thr drive transistor by is held constant, so the current flowing through the TFT 211 does not change.

[0196] Accordingly, the current flowing through the EL light emitting element 214 also does not change. Even if the I-V characteristic of the EL light emitting element 214 deteriorates, the current corresponding to the input voltage Vin constantly flows and therefore the past problem can be solved. [0197] In addition, by raising the on voltage of the gate of the TFT 213, it is possible to suppress variation in the resistance value due to variation in the threshold value Vth of the TFT 213.

[0198] Note that, in FIG. 13, the potential of the cathode electrode of the light emitting element 214 is made the ground potential GND, but this may be made any other potential as well.

[0199] Further, as shown in FIG. 16, the transistors of the pixel circuits need not be n-channel transistors. p-channel TFTs 221 to 223 may also be used to form each pixel circuit. In this case, the power source is connected to the anode side of the EL light emitting element 224, while the TFT 221 as the drive transistor is connected to the cathode side.

[0200] Further, the TFT 212 and TFT 213 as the switching transistors may also be transistors of different polarities from the TFT 211 as the drive transistor.

[0201] Here, the pixel circuit 201 according to the second embodiment and the pixel circuit 101 according to the first embodiment explained above will be compared.

[0202] The basic difference between the pixel circuit 201 according to the second embodiment and the pixel circuit 101 according to the first embodiment lies in the difference in the position of connection of the TFT 213 and TFT 113 as the switching transistors.

[0203] In general, the I-V characteristic of an organic EL element ends up deteriorating along with elapse. However, in the pixel circuit 101 according to the first embodiment, the potential difference Vs between the gate and source of the TFT 111 is held constant, so the current flowing through the TFT 111 is constant, therefore even if the I-V characteristic of the organic EL element deteriorates, the luminance is held.

[0204] In the pixel circuit 101 according to the first embodiment, when the TFT 112 is off and the TFT 113 is on, the source potential Vs of the drive transistor TFT 111 becomes the ground potential and the organic EL element 114 does not

emit light and enters a non-emitting period. Simultaneously, the first electrode (one side) of the pixel capacitor also becomes the ground potential GND. However, even in the non-emitting period, the gate-source voltage continues to be held and current flows in the pixel circuit 101 from the power source (Vcc) to the GND.

[0205] In general, an organic EL element has an emitting period and a non-emitting period. The luminance of a panel is determined by the product of the intensity of the emission and the emitting period. Usually, the shorter the emitting period, the better the moving picture characteristics become, so it is preferable to use the panel in a short emitting period. To obtain the same luminance as with when shortening the emitting period, it is necessary to raise the intensity of the emission of the organic EL element and necessary to run a greater current through the drive transistor.

[0206] Here, the pixel circuit 101 according to the first embodiment will be considered further.

[0207] In the pixel circuit 101 according to the first embodiment, as explained above, current flows even during the non-emitting period. Therefore, if shortening the emitting period and raising the amount of current run, current continuously flows even during the non-emitting period, so the current consumption increases.

[0208] Further, in the pixel circuit 101 according to the first embodiment, power source potential VVCC and ground potential GND lines are necessary in the panel. Therefore, it is necessary to lay two types of lines inside the panel at the TFT side. The Vcc and GND have to be laid by a low resistance to prevent a voltage drop. Accordingly, if laying two types of lines, the layout area of the lines has to be increased. For this reason, if the pitch between pixels becomes smaller along with the higher definition of panels, laying of the transistors etc. is liable to become difficult. Simultaneously, the regions where the Vcc lines and GND lines overlap in the panel are liable to increase and the improvement of the yield is liable to be kept down.

[0209] As opposed to this, according to the pixel circuit 201 according to the second embodiment, the effects of the above first embodiment can be obtained of course and also the effects of reduction of the consumed current and lines and improvement of the yield can be obtained.

[0210] According to the second embodiment, source-follower output with no deterioration in luminance even with a change in the I-V characteristic of an EL light emitting element along with elapse becomes possible.

[0211] A source-follower circuit of n-channel transistors becomes possible, so it is possible to use an n-channel transistor as a drive element of an EL light emitting element while using current anode-cathode electrodes.

[0212] Further, it is possible to configure transistors of a pixel circuit by only n-channel transistors and possible to use the a-Si process in the fabrication of the TFTs. Due to this, a reduction of the cost of TFT boards becomes possible.

[0213] Further, according to the second embodiment, it is possible to slash the number of GND lines at the TFT side and layout of the surrounding lines and layout of the pixels become easier.

[0214] Further, it is possible to slash the number of GND lines at the TFT side, possible to eliminate the overlap of the GND lines and Vcc lines at the TFT board, and possible to improve the yield.

[0215] Further, it is possible to slash the number of GND lines at the TFT side, possible to eliminate the overlap of the

GND lines and Vcc lines at the TFT board so as to lay the Vcc lines at a low resistance, and possible to obtain an image quality of a high uniformity.

#### Third Embodiment

[0216] FIG. 17 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a third embodiment.

[0217] FIG. 18 is a circuit diagram of the concrete configuration of a pixel circuit according to the third embodiment in the organic EL display device of FIG. 17.

[0218] The display device 200A according to the third embodiment differs from the display device 200 according to the second embodiment in the position of connection of the capacitor C211 as the pixel capacitor Cs in the pixel circuit. [0219] Specifically, in the pixel circuit 201 according to the second embodiment, the capacitor C211 is connected between the gate of the TFT 211 as the drive transistor and the anode side of the EL light emitting element 214.

[0220] As opposed to this, in the pixel circuit 201A according to the third embodiment, the capacitor C211 is connected between the gate and source of the TFT 211 as the drive transistor. Specifically, a first electrode of the capacitor C211 is connected to the connection point (node ND211A) of the source of the TFT 211 and the TFT 213 as the switching transistor and a second electrode is connected to the node ND212.

[0221] The rest of the configuration is similar to that of the second embodiment explained above.

[0222] Next, the operation of the above configuration will be explained focusing on the operation of a pixel circuit with reference to FIGS. 19A to 19E and FIGS. 20A to 20F.

[0223] First, at the ordinary emitting state of the EL light emitting element 214, as shown in FIGS. 20A to 20D, the scanning signals ws[201], ws[202], . . . to the scanning lines WSL201, WSL202, . . . are selectively set to the low level by the write scanner 204, and the drive signals ds[201], ds[202], . . . to the drive lines DSL201, DSL202, . . . are selectively set to the high level by the drive scanner 205.

[0224] As a result, in the pixel circuit 201A, as shown in FIG. 19A, the TFT 212 is held in the off state and the TFT 213 is held in the on state.

[0225] At this time, the current Ids flows to the TFT 211 as the drive transistor and the EL light emitting element 214.

[0226] Next, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 20A to 20D, the scanning signals ws[201], ws[202], ... to the scanning lines WSL201, WSL202, ... are held at the low level by the write scanner 204, and the drive signals ds[201], ds[202], ... to the drive lines DSL201, DSL202, ... are selectively set to the low level by the drive scanner 205.

[0227] As a result, in the pixel circuit 201A, as shown in FIG. 19B, the TFT 212 is held in the off state and the TFT 213 is turned off

[0228] At this time, the potential held at the EL light emitting element 214 falls since the source of supply disappears. The potential falls to the threshold voltage Vth of the EL light emitting element 214. However, since off current also flows to the EL light emitting element 214, if the non-emitting period continues, the potential will fall to GND.

[0229] On the other hand, the TFT 211 as the drive transistor is held in the on state since the gate potential is high. As shown in FIG. 20F, the source potential Vs of the TFT 211 is boosted to the power source voltage Vcc. This boosting is

performed in a short period. After boosting to the Vcc, no current is supplied to the TFT 211.

[0230] That is, in the pixel circuit 201A of the third embodiment, it is possible to operate without the supply of current in the pixel circuit during the non-emitting period and therefore possible to suppress the power consumption of the panel.

[0231] Next, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 20A to 20D, the drive signals ds[201], ds[202],... to the drive lines DSL201, DSL202,... are held at the low level by the drive scanner 205, and the scanning signals ws[201], ws[202],... to the scanning lines WSL201, WSL202,... are selectively set to the high level by the write scanner 204.

[0232] As a result, in the pixel circuit 201A, as shown in FIG. 19C, the TFT 213 is held in the off state and the TFT 212 is turned on. Due to this, the input signal (Vin) propagated to the data line DTL201 by the horizontal selector 203 is written into the capacitor C211 as the pixel capacitor Cs.

[0233] At this time, as shown in FIG. 20F, since the source Vs of the TFT 213 as the switching transistor is the power source potential Vcc, the capacitor C211 as the pixel capacitor Cs is held at a potential equal to (Vin-Vcc) with respect to the voltage Vin of the input signal.

[0234] After this, in the non-emitting period of the EL light emitting element 214, as shown in FIGS. 20A to 20D, the drive signals ds[201], ds[202],... to the drive lines DSL201, DSL202,... are held at the low level by the drive scanner 205, and the scanning signals ws[201], ws[202],... to the scanning lines WSL201, WSL202,... are selectively set to the low level by the write scanner 204.

[0235] As a result, in the pixel circuit 201A, as shown in FIG. 19D, the TFT 212 is turned off and the write operation of the input signal to the capacitor C211 as the pixel capacitor ends.

[0236] After this, as shown in FIGS. 20A to 20D, the scanning signals ws[201], ws[202], . . . to the scanning lines WSL201, WSL202, . . . are held at the low level by the write scanner 204, and the drive signals ds[201], ds[202], . . . to the drive lines DSL201, DSL202, . . . are selectively set to the high level by the drive scanner 205.

[0237] As a result, in the pixel circuit 201A, as shown in FIG. 19E, the TFT 213 is turned on.

[0238] By turning the TFT 213 on, current flows to the EL light emitting element 214 and the source potential of the TFT 211 falls. The source potential of the TFT 211 as the drive transistor fluctuates, but despite this, since there is a capacitor between the gate and source of the TFT 211, the other transistors etc. are not connected, so the gate-source voltage of the TFT 211 is constantly held at (Vin-Vcc). At this time, the TFT 211 as the drive transistor is driven in the saturated region, so the current Ids flowing through the TFT 211 becomes the value shown in the above equation 1. This is the gate-source voltage Vgs of the drive transistor, that is, (Vin-Vcc).

[0239] That is, the current flowing through the TFT 211 can be said to be determined by the Vin.

[0240] Due to the above, even if the EL light emitting element 214 deteriorates in its I-V characteristic along with the increase in the emitting period, in the pixel circuit 201A of the third embodiment, the potential of the node ND211A falls while the potential between the gate and source of the TFT 211 as the drive transistor is held constant, so the current flowing through the TFT 211 does not change.

[0241] Accordingly, the current flowing through the EL light emitting element 214 also does not change. Even if the

I-V characteristic of the EL light emitting element 214 deteriorates, the current corresponding to the input voltage Vin constantly flows and therefore the past problem can be solved. [0242] In addition, since there is no transistor etc. other than the pixel capacitor Cs between the gate and source of the TFT 211, variation in the threshold value Vth will not cause any change of the gate-source voltage Vgs of the TFT 211 as the drive transistor like in the past system.

[0243] Note that, in FIG. 18, the potential of the cathode electrode of the light emitting element 214 is made the ground potential GND, but this may be made any other potential as well. Rather, making this the negative power source enables the potential of the Vcc to be lowered and enables the potential of the input signal voltage to be lowered. Due to this, design without burdening the external IC becomes possible. [0244] Further, since no GND lines are required, the number of input pins to the panel can be slashed and pixel layout also becomes easier. In addition, since there are no longer intersecting parts of the Vcc and GND lines in the panel, the yield can also be easily improved.

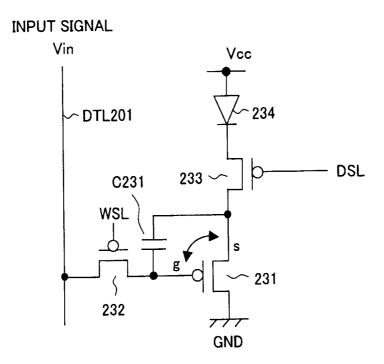

[0245] Further, as shown in FIG. 21, the transistors of the pixel circuits need not be n-channel transistors. p-channel TFTs 231 to 233 may also be used to form each pixel circuit. In this case, the power source is connected to the anode side of the EL element 234, while the TFT 231 as the drive transistor is connected to the cathode side.

[0246] Further, the TFT 212 and TFT 213 as the switching transistors may also be transistors of different polarities from the TFT 211 as the drive transistor.

[0247] According to the third embodiment, source-follower output with no deterioration in luminance even with a change in the I-V characteristic of an EL light emitting element along with elapse becomes possible.

[0248] A source-follower circuit of n-channel transistors becomes possible, so it is possible to use an n-channel transistor as a drive element of an EL light emitting element while using current anode-cathode electrodes.

**[0249]** Further, it is possible to configure transistors of a pixel circuit by only n-channel transistors and possible to use the a-Si process in the fabrication of the TFTs. Due to this, a reduction of the cost of TFT boards becomes possible.

[0250] Further, according to the third embodiment, it is possible to slash the number of GND lines at the TFT side and layout of the surrounding lines and layout of the pixels become easier.

[0251] Further, it is possible to slash the number of GND lines at the TFT side, possible to eliminate the overlap of the GND lines and Vcc lines at the TFT board, and possible to improve the yield.

[0252] Further, it is possible to slash the number of GND lines at the TFT side, possible to eliminate the overlap of the GND lines and Vcc lines at the TFT board so as to lay the Vcc lines at a low resistance, and possible to obtain an image quality of a high uniformity.

## Fourth Embodiment

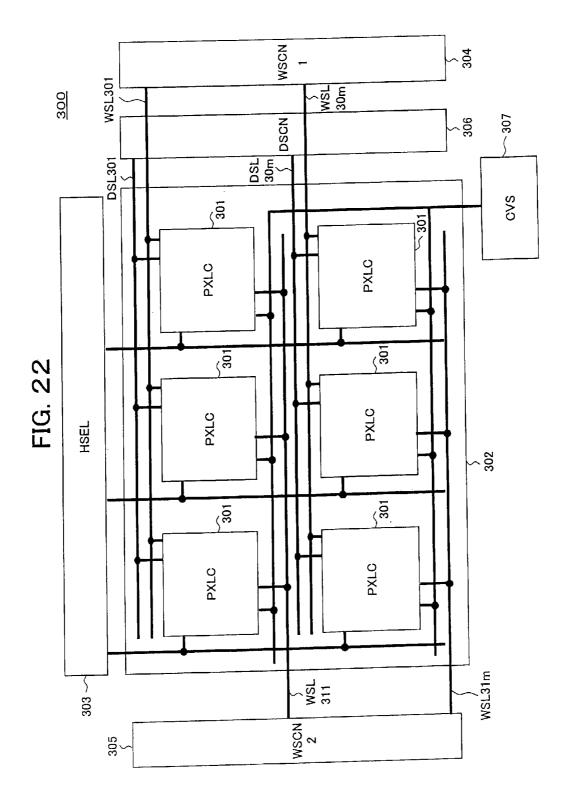

[0253] FIG. 22 is a block diagram of the configuration of an organic EL display device employing a pixel circuit according to a fourth embodiment.

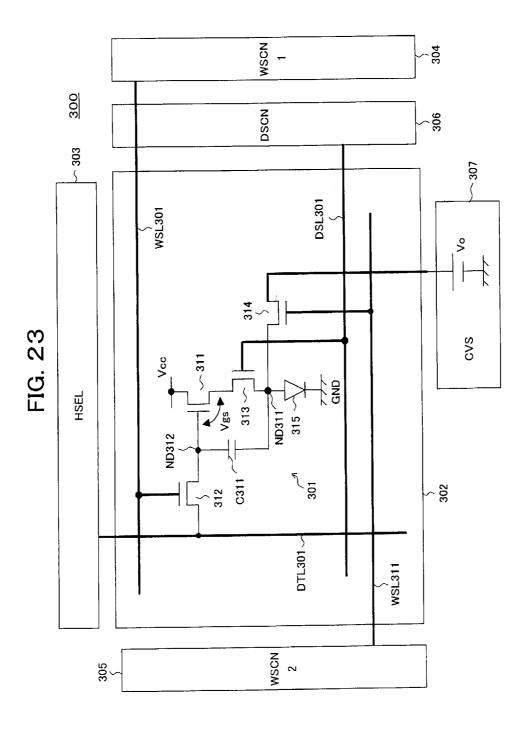

[0254] FIG. 23 is a circuit diagram of the concrete configuration of a pixel circuit according to the fourth embodiment in the organic EL display device of FIG. 22.

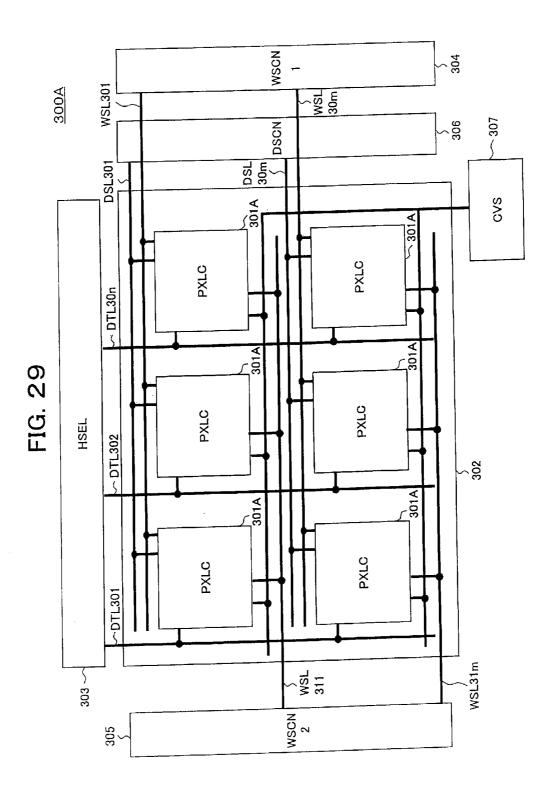

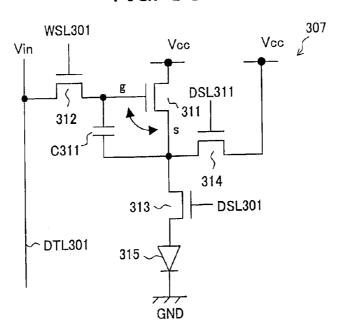

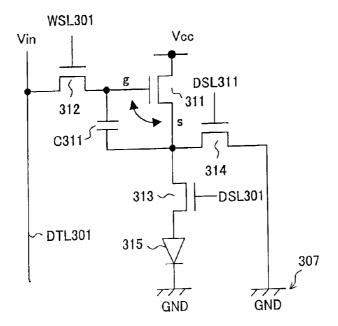

[0255] The display device 300, as shown in FIG. 22 and FIG. 23, has a pixel array portion 302 having pixel circuits

(PXLC) 301 arranged in an m×n matrix, a horizontal selector (HSEL) 303, a first write scanner (WSCN1) 304, a second write scanner (WSCN2) 305, a drive scanner (DSCN) 36, a constant voltage source (CVS) 307, data lines DTL301 to DTL30n selected by the horizontal selector 303 and supplied with a data signal in accordance with the luminance information, scanning lines WSL301 to WSL30m selectively driven by the write scanner 304, scanning lines WSL311 to WSL31m selectively driven by the write scanner 305, and drive lines DSL301 to DSL30m selectively driven by the drive scanner 306.

[0256] Note that while the pixel circuits 301 are arranged in an  $m \times n$  matrix in the pixel array portion 302, FIG. 22 shows an example wherein the pixel circuits are arranged in a 2 (=m)×3 (=n) matrix for the simplification of the drawing.

[0257] Further, in FIG. 23 as well, the concrete configuration of one pixel circuit is shown for simplification of the drawing.

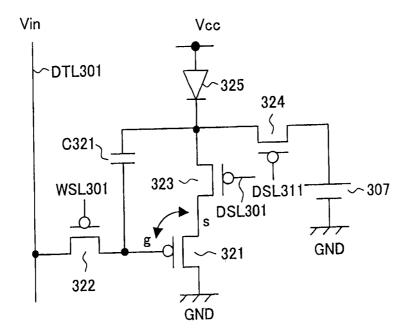

[0258] Each pixel circuit 301 according to the fourth embodiment has, as shown in FIG. 23, an n-channel TFT 311 to TFT 314, a capacitor C311, a light emitting element 315 made of an organic EL element (OLED), and nodes ND311 and ND312.

[0259] Further, in FIG. 23, DTL301 indicates a data line, WSL301 and WSL311 indicate scanning lines, and DSL301 indicates a drive line.

[0260] Among these components, the TFT 311 configures the field effect transistor according to the present invention, the TFT 312 configures the first switch, the TFT 313 configures the second switch, the TFT 314 configures the third switch, and the capacitor C311 configures the pixel capacitance element according to the present invention.

[0261] Further, the scanning line WSL301 corresponds to the first control line according to the present invention, the drive line DSL301 corresponds to the second control line, and the scanning line WSL311 corresponds to the third control line.

[0262] Further, the supply line of the power source voltage Vcc (power source potential) corresponds to the first reference potential, while the ground potential GND corresponds to the reference potential.

[0263] In each pixel circuit 301, a source and a drain of the TFT 313 are connected between a source of the TFT 311 and an anode of the light emitting element 315, a drain of the TFT 311 is connected to the power source potential Vcc, and a cathode of the light emitting element 315 is connected to the ground potential GND. That is, the TFT 311 as the drive transistor, the TFT 313 as the switching transistor, and the light emitting element 315 are connected in series between the power source potential Vcc and the ground potential GND. Further, the connection point of the anode of the light emitting element 315 and the TFT 313 constitutes a node ND311.